Esta semana, durante la conferencia SEMICON West celebrada en San Francisco, EE.UU., los responsables de ingeniería de Intel han presentado novedades respecto a las capacidades de encapsulado avanzadas de Intel y presentado nuevos bloques de componentes, incluyendo usos innovadores de EMIB y Foveros, junto con una nueva tecnología de conexión omnidireccional (Omni-Directional Interconnect, ODI). Combinadas con las tecnologías de procesamiento de primera línea de Intel, las nuevas capacidades de encapsulado favorecerán innovaciones de clientes y el progreso de los sistemas informáticos del futuro.

El encapsulado de los chips siempre ha desempeñado un papel crítico, aunque a menudo subestimado, en la cadena de suministro de los componentes electrónicos. Como interfaz física entre el procesador y la placa base, la capsula proporciona una zona de contacto entre las señales eléctricas del chip y la fuente de alimentación. A medida que el sector de la electrónica avanza en la transición hacia una era centrada en los datos, el encapsulado avanzado desempeñará un papel aun mayor que en el pasado.

Más que el paso final en el proceso de fabricación, el encapsulado se está convirtiendo rápidamente en el catalizador de la innovación de productos. Las técnicas avanzadas de encapsulado permiten la integración de múltiples motores informáticos en diversos procesos tecnológicos con parámetros de rendimiento similares al de un único cubo, pero con una gama de plataformas que supera ampliamente las limitaciones de tamaño e integración de un único cubo. Estas tecnologías mejorarán el rendimiento, consumo y superficie a nivel de productos, al tiempo que permitirán rediseñar por completo la arquitectura de los sistemas.

Durante SEMICON West, Intel ha revelado tres nuevas tecnologías que abrirán una nueva dimensión en la arquitectura de productos:

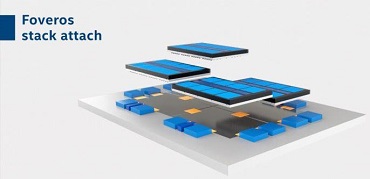

Co-EMIB: las tecnologías EMIB y Foveros de Intel aprovechan las interconexiones de alta densidad para facilitar amplios anchos de banda con bajo consumo, con una densidad de I/O igual o mejor que los enfoques alternativos. La nueva tecnología Co-EMIB de la compañía permite enlazar aún más capacidad y rendimiento informático. Gracias a Co-EMIB, es posible interconectar dos o más elementos Foveros para obtener un rendimiento prácticamente idéntico al de un único chip. Los diseñadores también pueden conectar elementos analógicos, memoria y demás con un ancho de banda muy amplio y un consumo muy bajo.

ODI: la nueva tecnología de interconexión omnidireccional (Omni-Directional Interconnect) de Intel proporciona aún más flexibilidad para la comunicación entre chiplets en una misma capsula. El chip principal puede comunicarse horizontalmente con otros chiplets, de un modo similar a EMIB. También puede comunicarse verticalmente mediante vías a través del silicio (Through-Silicon Vias, TSVs) en el cubo inferior de la base, de un modo similar a Foveros. Además, ODI aprovecha las amplias vías verticales para favorecer la transmisión de la alimentación al cubo superior directamente desde el substrato de la capsula. Con un tamaño sensiblemente mayor que las TSVs tradicionales, las amplias vías ofrecen menor resistencia, proporcionando una alimentación más robusta simultáneamente con un amplio de banda mayor y una latencia baja gracias al apilado. Al mismo tiempo, este enfoque reduce el número de TSVs requeridas en el cubo de la base, liberando más superficie para transistores activos y optimizando el tamaño del cubo.

MDIO: basándose en su interconexión de nivel PHY, Advanced Interface Bus (AIB), Intel ha revelado una nueva interfaz entre cubos denominada MDIO. La tecnología permite un enfoque modular en el diseño de sistemas mediante una librería de bloques de propiedad intelectual de chiplets. MDIO proporciona una mayor eficiencia energética y más del doble de velocidad de pin y densidad de ancho de banda que AIB.

Colectivamente, estas tecnologías constituyen herramientas complementarias de un conjunto muy potente. En combinación con las tecnologías de procesos de Intel, representan la paleta de colores subyacente que facilita la creatividad de los arquitectos de chips, permitiéndoles la libertad de concebir nuevos productos.